コンピュータシステム(1)

コンピュータ構成要素

プロセッサ

コンピュータの頭脳。「中央演算処理装置」、「CPU」とも呼ばれる

コンピュータの種類

| 名称 | 説明 | 用途 |

|---|---|---|

| スーパーコンピュータ (スパコン) | 加賀機技術計算などの高速処理を目的とした、最も高速、高性能なコンピュータ | 気象予測、航空管制、宇宙開発など |

| 汎用コンピュータ (メインフレーム) | 事務処理、科学技術計算の両方に使用できように設計されたコンピュータ | 座席予約、銀行のオンラインシステム等 |

| ワークステーション | 専門的な事務に用いられる高性能なコンピュータ、CAD/CAMやEWS(科学技術計算等に利用)、オフィスワークステーション(事務処理、情報管理等に利用)分る英。主にLANに接続しサーバとして利用 | ソフトウェア開発、CAD/CAM、サーバなど |

| パーソナル コンピュータ | 個人用にさまざまな用途で使用されるコンピュータ | インターネット、文書作成、表計算等 |

| FDA (携帯情報端末) | 持ち運びを前提とした手のひらサイズのパソコン | インターネット、個人情報管理など |

マイクロコンピュータ(マイコン)

マイクロコンピュータ(マイコン)

制御を目的に使用される機器組込用の超小型のコンピュータシステムのこと。制御用のコンピュータとして、洗濯機、自動車、産業用ロボット、POSシステムなどさまざまな機器に組み込まれている

シングルチップマイコン

シングルチップマイコン

ひとつの集積回路に演算や入出力、記憶機能を持ったマイクロコンピュータのこと

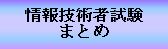

コンピュータの構成

| 装置 | 働き | 主な装置 |

|---|---|---|

| 制御装置 | プログラムを解釈し、各装置を管理・制御する | CPU |

| 演算装置 | プログラムの命令に従って処理・計算する | |

| 記憶装置 | プログラムやデータを記憶する。「メインメモリ(主記憶装置)」「補助記憶装置」に分けられる | メインメモリ:DRAM、SRAM 補助記憶装置:HDD、USBメモリ |

| 入力装置 | メインメモリにデータを入力する | キーボード、マウス |

| 出力装置 | メインメモリのデータを出力(表示・印刷)する | ディスプレイ、プリンタ |

CPUの構成

コンピュータでは主記憶装置にあるプログラムやデータをひとつずつCPUに読み込み、プログラムの命令を処理したうえで各装置に伝達する

演算装置

プログラムの命令に従い、主記憶装置のデータに対して演算を行う。加算や減算などの四則演算やAND演算やOR演算などの論理演算を行う「算術論理演算装置」などから構成される

算術論理演算装置(ALU)

算術論理演算装置(ALU)

通常、算術論理演算装置には加算器と補数器が組み込まれている

制御装置

デコーダによってプログラムを解釈して他の装置に命令を出す

デコーダ

デコーダ

プログラムの命令を解読する装置のこと。「命令解読器」、「復号器」

レジスタ

処理中の命令などを一時的に記憶する領域のこと。記憶する内容によってさまざまなレジスタがある

| 名称 | 説明 |

|---|---|

| 命令レジスタ | 実行する命令を記憶する |

| 命令アドレスレジスタ | 次に実行する命令に関する情報(主記憶装置上の命令の格納場所)を記憶する。「命令カウンタ」「プログラムカウンタ」「逐次制御カウンタ」 |

| インデックスレジスタ | 主記憶装置上のデータの格納場所を導き出すときに、指標となる値を記憶する。「指標レジスタ」 |

| ベースレジスタ | プログラムの先頭アドレスを記憶する |

| アキュムレータ | 演算対象や演算結果を記憶する |

| 汎用レジスタ | さまざまな目的に利用されるが、通常は演算対象や演算結果を記憶する |

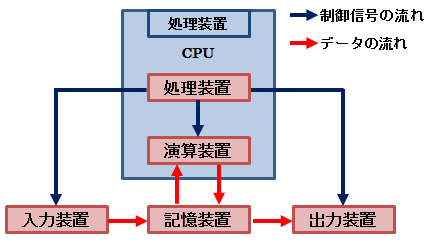

CPUの動作の仕組み

命令の動作手順

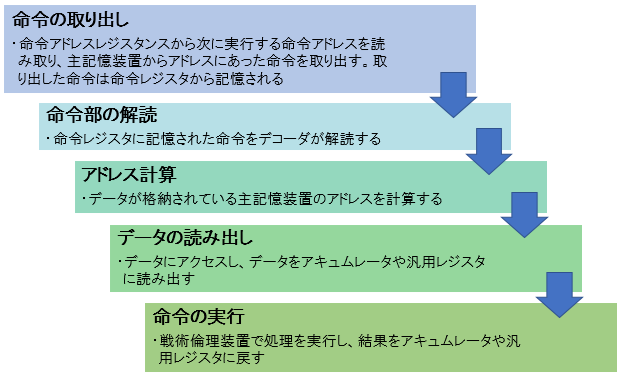

命令の構成

命令はCPUで理解し、実行できる言語(機械語)である必要がある。デコーダでは、機械語の命令を読み取り、解析することで処理を行っている

命令の形式はCPUの種類によって異なるが、一般的には次のような構成になっている

| 名称 | 説明 |

|---|---|

| 算術演算命令 | 整数データに対して四則演算を行う |

| 論理演算命令 | 論理演算を行うもので、論理積、論理和、排他的論理和、否定などがある |

| 転送命令 | レジスタ間や主記憶装置間、レジスタと主記憶装置間でデータの転送を行う |

| 比較命令 | 比較対象の比較を行う |

| 分岐命令 | 次に実行される命令をジャンプし、他の命令に移動する 条件分岐命令:条件に合っているかどうかを判断した結果によって、次に実行する命令を決める 無条件分岐命令:無条件で分岐する |

| シフト命令 | データを構成するビットの列を左右に移動する |

| 入出力命令 | 入出力装置と主記憶装置間でのデータ転送を行う |

アドレス指定方式(アドレス装飾、アドレッシング)

命令のアドレス部をもとに、データが格納されている「実効アドレス」を指定する方式のこと

即値アドレス指定方式

即値アドレス指定方式

命令内のアドレス部の値を処理対象のデータとして使用する方式

直接アドレス指定方式

直接アドレス指定方式

命令内のアドレス部の値を実効アドレスとする方式

間接アドレス指定方式

間接アドレス指定方式

命令内のアドレス部が参照する主記憶装置の値を実効アドレスとする方式

インデックスアドレス指定方式

インデックスアドレス指定方式

命令内のアドレス部の値のインデックスレジスタの値を加算して実効アドレスとする方式

ベースアドレス指定方式

ベースアドレス指定方式

命令内のアドレス部の値にベースレジスタの値を加算して実効アドレスとする方式

相対アドレス指定方式

相対アドレス指定方式

命令内のアドレス部の値に命令アドレスレジスタの値を加算して実効アドレスとする方式

割込み

CPUでは基本的に主記憶装置上の命令を順番に実行するが、命令を実行中に、プログラムやハードウェアのエラー等突然も問題が発生した場合、それぞれの問題に対応したプログラムが呼び出される。これを「割込み」という

割込みが起こると、CPUは実行中の命令を中断し、問題解決に必要な命令を実行し、その後問題が解決されると、CPUは割込み前に行っていた命令に戻る

| 名称 | 説明 |

|---|---|

| 内部 割込み | プログラムの処理やエラー等、実行中のプログラム(CPU内部)が原因で行われる割込み ・SVC割込み:入出力を実行したり、保護されたメモリ領域にアクセスしたりした場合に発生する(スーパバイザコール) |

| 外部 割込み | CPU外部の周辺機器が原因で行われる割込み ・タイマ割込み:CPUの割り当て時間が一定時間を経過した場合に発生する ・入出力割込み:入出力処理が終了したり、入出力装置に障害が発生した場合に発生する |

CPUの性能

一度に処理するデータ量によって16ビットCPU、32ビットCPU、64ビットCPUなどに分類される

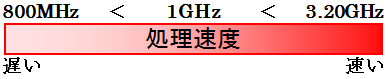

クロック周波数

●1秒間に送られる信号の回数のこと

●同じビット数のCPUでもクロック周波数によって処理能力が異なる

●「CPUの名称」+「MHz」or「GHz」で表現

(例:2.93GHzのCPU ⇒ 1秒間に2.93億回の動作)

| 1秒間に実行できる命令数を求める計算式 CPUのクロック周波数 ÷ 1命令を実行するのに必要なクロック数 |

| CPUの1クロックあたりの処理時間を求める計算式 1秒 ÷ CPUのクロック周波数 |

CPI

●CPUの処理能力を表す単位

●1命令を実行するときに必要なクロック数を示す

(例:1CPIのCPU ⇒ 1命令を1クロック

2CPIのCPU ⇒ 1命令を2クロック)

| CPUの1命令あたりの実行時間を求める計算式 CPUのクロックあたりの処理時間 × CPI |

MIPS

●CPUの処理能力を表す単位

●1秒間に実行できる命令の数

(例:1MIPSのCPU ⇒ 1秒間に100万個の命令(106命令/秒)を処理できる)

| CPUのの命令実行数(MIPS)を求める計算式 1秒 ÷ 1命令を実行するのに必要な時間 ÷ 106 (命令/秒) |

命令ミックス

命令によって異なるクロック周波数を実際の作業内容に合ったCPUの処理能力を計測する標準的な命令の組み合わせのこと

| 命令ミックスを使ってCPUの処理能力を求める計算式 命令1の実行速度(1命令あたりの実行時間) × 出現比率 + 命令2の実行速度(1命令あたりの実行時間) × 出現比率 ・・・ |

FLOPS

FLOPS

CPUの処理速度を表す単位。1秒間に実行できる浮動小数点数演算の数を示す

1FLOPSのCPUは1秒間に1回の浮動小数点数演算ができる

CPUのアーキテクチャ

アーキテクチャ

アーキテクチャ

ハードウェアやソフトウェアの基本設計や設計思想のこと

RISC(リスク)

使用頻度の高い命令を固定長方式で単純化すること。パイプライン方式の効率を高め、動作速度の向上や処理速度の短縮を図るもの。パソコンやワークステーションなどのCPUで採用(IBM社のPowerPCシリーズなど)。ハードウェアのカイロで制御信号を発生させる「ワイヤドロジック(結線論理)制御方式」が用いられる

CISC(シスク)

可変長方式の複雑な命令をCPUが理解できるようにすることで、全体的に高性能化を図るもの。スーパーコンピュータや汎用コンピュータなどのCPUで採用(Intel社のx86シリーズなど)。1命令中で行う処理が複雑なため、マイクロプログラムを組み合わせた「マイクロプログラム制御方式」が用いられる。機能の追加・変更がマイクロコード(単純な命令)の変更だけで行えるので、命令の追加・変更が容易

マイクロプログラム

マイクロプログラム

基本動作を記述したマイクロコードでできたプログラムのこと

CPUの高速化技術

1つの命令の処理は、

1.命令取り出し(Instruction Fetch)

2.命令解読(Instruction Decode)

3.オペランドアドレス計算(Operand Addressing)

4.命令実行(Execute)

5.実行結果の書き込み(Store)

などのように、複雑な段階からなるサイクルで構成されている。通常は、前の命令のサイクルが完全に終わらないと、次の命令を処理し始めることはできない。しかし、各段階の処理機構を独立して動作させることにより、流れ作業的に、前の命令のサイクルが終わる前に次の命令を処理し始めることが出来る

パイプライン方式

CPUの内部動作をいくつかのステージに分割して、ステージ単位で並行処理を行う仕組み

逐次処理

逐次処理

主記憶装置上における命令の処理課程をひとつずつ順番に行うこと

スーパーパイプライン方式

パイプライン方式の各ステージをさらに細分化して、パイプラインの動作の効率を向上させ、高速を図る技術

スーパースカラ方式

複数のパイプラインを使って同時に複数の命令を処理することで高速化を図る技術

VLIW

依存関係にない複数の短い命令をひとつの命令にまとめて同時に実行することで高速化を図る技術のこと。命令の長さは一定なので、複数の命令をまとめたときに長さが足りないときは“何もしない”という命令が挿入される。コンパイラが機械語のプログラム(目的プログラム)を生成する段階で、それぞれの命令をどの演算器を使用するかを割り当てる

マルチプロセッサシステムと並列処理

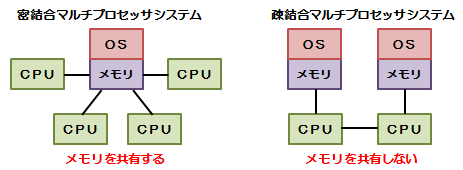

コンピュータの処理能力を向上させるため、システムによってはCPUを複数持つものもある。CPUを複数持つシステムを「マルチプロセッサシステム」「並列コンピュータ」と呼ぶ

マルチプロセッサシステムの種類

密結合マルチプロセッサシステム

密結合マルチプロセッサシステム

複数のCPUがひとつの主記憶装置とOSを共有する。複数のCPUをバスで結合してひとまとめにしたシステム

疎結合マルチプロセッサシステム

疎結合マルチプロセッサシステム

複数のCPUが主記憶装置とOSを個別に持ち、複数のコンピュータを結合してひとまとまりのシステムにしたもの「コンピュータクラスタ」とも呼ぶ

アムダールの法則

アムダールの法則

コンピュータの一部の性能を改善したとき、全体の性能の向上は、改善した性能が利用される場合に限る

CPUのシステム構成

| 名称 | 説明 |

|---|---|

| SISD(シスド) | ひとつのCPUを搭載したコンピュータ上で、ひとつの命令でひとつのデータを処理する方式 |

| SIMD(シムド) | ひとつのCPUを搭載したコンピュータ上で、ひとつの命令で複数のデータをまとめて処理する方式 |

| MISD(ミスド) | 複数のCPUがお互いに同期を取りながら、ひとつのデータを処理する方式 |

| MIMD(ミムド) | 複数のCPUがお互いに同期をとりながら、複数のデータを処理する方式 |