コンピュータシステム(1)

コンピュータ構成要素

ハードウェアの高速化技術

| プロセッサ (CPU) | パイプライン/スーパーパイプライン |

|---|---|

| スーパースカラ | |

| RISC | |

| VLIW | |

| マルチプロセッサ/マルチコア | |

| アウトオブオーダー実行 | |

| メモリ | キャッシュメモリ |

| メモリインタリーブ | |

| RAIDO(ストライピング) |

CPU

CPUの動作

割込み

命令を実行中に、プログラムやハードウェアのエラー等、突然の問題が生じた場合、それぞれの問題に対応したプログラムが呼び出されること。割込みが発生すると、CPUは実行中の命令を中断して、問題解決に必要な命令を実行し、問題解決後、割込み前の命令に戻る

| 内部割込み | プログラムの処理やエラー等実行中のプログラム(CPU内部)が原因で行われる割込み ●SVC割込み:入出力処理を実行したり、保護されたメモリ領域にアクセスしたりした場合に発生する(スーパバイザコール) ●プログラム割込み:特権命令割込み、演算例外割込み |

|---|---|

| 外部割込み | CPU外部の周辺機器が原因で行われる割込み ●タイマ割込み:CPUの割当て時間が一定時間を経過した場合に発生 ●入出力処理が終了したり、入出力装置に障害が発生した場合に発生 |

多重割込み

多重割込み

割込み処理を行っている時に別の割込みが発生した状況。割込みの種類の優先順位に従って制御を行う

性能

クロック周波数

●S1秒間に送られる信号回数のこと

●同じビット数のCPUでもクロック周波数によっても処理能力が異なる

●「CPUの名称」+「MHz」or「GHz」で表現

(例:2.93GHzのCPU ⇒ 1秒間に2.93億回の動作)

| 1秒間に実行できる命令数 CPUのクロック周波数÷1命令を実行するのに必要なクロック数 |

CPI

CPI

●CPUの処理速度を表す単位

●1命令を実行するときに必要なクロック数を示す

(例:2CPIのCPU ⇒ 1命令を2クロックで実行)

| CPUの1命令あたりの実行時間を求める CPUの1クロックあたりの処理時間×CPI |

MIPS

MIPS

●CPUの処理速度を表す単位

●1秒間に実行できる命令

(例:1MIPSのCPU ⇒ 1秒間に100万個の命令(106命令/秒)を処理)

| CPUの命令実行数(MIPS)を求める 1秒÷1命令を実行するのに必要な時間÷106(命令/秒) |

FLOPS(プロップス、Floationg-point Operationg Per Second)

FLOPS(プロップス、Floationg-point Operationg Per Second)

コンピュータの性能指標の一つ。1秒間に浮動小数点演算が何回できるかという能力を理論的・実際的(実験的)に表した値のこと。物理現象のシミュレーションや科学技術計算を行うスーパーコンピュータ等の性能指標として用いられることが多い。

ベクトルコンピュータ

ベクトルコンピュータ

ベクトル演算を行うことができるコンピュータのこと。狭義では、ベクトル演算のための高性能でパイプライン化された実行ユニットを持ち、その演算能力を可能な限り発揮できるように設計されたスーパーコンピュータ

プロセッサの高速化

1つの命令の処理は、

1.命令取り出し(Instruction Fetch)

2.命令解読(Instruction Decode)

3.オペランドアドレス計算(Operand Addressing)

4.命令実行(Execute)

5.実行結果の書き込み(Store)

などのように、複雑な段階からなるサイクルで構成されている。通常は、前の命令のサイクルが完全に終わらないと、次の命令を処理し始めることはできない。しかし、各段階の処理機構を独立して動作させることにより、流れ作業的に、前の命令のサイクルが終わる前に次の命令を処理し始めることが出来る

パイプライン方式

CPUの内部動作をいくつかのステージに分割して、ステージ単位で並行処理を行う仕組み

| パイプライン制御方式の実行命令サイクル数 1命令のサイクル数+(命令数−1) |

スーパーパイプライン方式

パイプライン方式の各ステージをさらに細分化して、パイプラインの動作の効率を向上させ、高速を図る技術

パイプラインハザード

パイプラインハザード

マイクロプロセッサのパイプライン処理で発生する問題の一つで、命令間の依存関係などによりパイプライン処理を止めたりやり直さなければならなくなることある

いくつかの要因によって発生する

一般的にパイプラインハザードは、それが引き起こされる原因によって次の3種類に分類される

データハザード

データハザード

処理するデータの依存関係が原因で発生するハザード。後続の命令が直前の命令の実行結果を利用する場合などに発生する

構造ハザード

構造ハザード

複数の命令によるハードウェア資源(演算器やメモリなど)の競合によって発生するハザード。主にメモリアクセスの競合が発生した場合に発生する

制御ハザード

制御ハザード

命令の先読みを行っている処理中の分岐命令や割込み処理が原因で発生するハザード。次に実行すべき命令が判明するまでパイプラインへの読込みを停止したり、先読みした処理が無駄になることで処理効率が悪くなってしまう状態

レジスタ・リネーミング

レジスタ・リネーミング

コンピュータのプログラム内でレジスタを再利用しているために不必要な順序性が生じているのを、より多くの実在するレジスタを利用して再利用されているレジスタに割り当て、依存を無くす技術

遅延分岐

遅延分岐

制御依存によって生じるハザードが解消するまで、その分岐命令の実行を先延ばしにすることで、ハザードを解消する方法

投機実行

投機実行

プログラムが途中で条件分岐しているときに、分岐先を予測して分岐先の処理をあらかじめ実行しておくこと

分岐予測

分岐予測

パイプライン処理を行っているCPUでは、分岐が生じるとパイプラインにすでに設定されている命令を捨てる作業が必要となり、処理が遅くなる(命令ハザード)。プログラム実行の流れの中で条件分岐命令が分岐するかしないかを予測することにより、命令パイプラインの効果を可能な限り維持し、性能を高めるためのCPU内の機能・仕組み

アウトオブオーダー実行

アウトオブオーダー実行

プログラムに記述された命令の順番に関係なく、処理に必要なデータが揃った命令から実行する仕組み。先の命令処理に必要なデータが揃っていなくても、後の命令処理に必要なデータが揃っていた場合、後の命令から先に実行することができる。CPUの性能を向上するための技術のひとつ

スーパースカラ

複数のパイプラインを使って同時に複数の命令を処理することで高速化を図る技術。

VLIW

依存関係にない複数の短い命令をひとつの命令にまとめて同時に実行することで高速化を図る技術。命令の長さは一定なので、複数の命令をまとめたときに長さが足りないときは“何もしない”という命令が挿入される。VLIWプロセッサは、整数/論理演算ユニット、浮動小数点演算ユニット、分岐ユニットなどの複数のユニットを装備している。コンパイラが機械語のプログラム(目的プログラム)を生成する段階で、それぞれの命令をどの演算器を使用するかを割り当てる

マルチプロセッサと並列処理

マルチプロセッサ

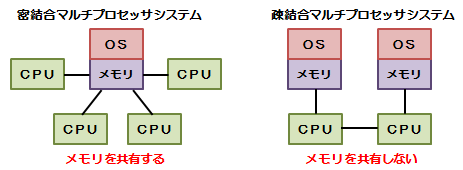

パイプライン処理やスーパースカラがあくまでも一つのプロセッサで並列処理を行い、スループットの向上を図っているのに対し、マルチプロセッサは、複数のCPUを搭載し、各CPUに処理を分散させることで処理性能の向上を図る。主記憶装置を共有するか否かで、密結合マルチプロセッサと疎結合マルチプロセッサに分類される

密結合マルチプロセッサ

密結合マルチプロセッサ

複数のCPUがひとつの主記憶装置とOSを共有する。複数のCPUをバスで結合してひとまとめにしたシステム。パソコンサーバやUNIXサーバによく見られる方式

疎結合マルチプロセッサ

疎結合マルチプロセッサ

複数のCPUが主記憶装置とOSを個別に持ち、複数のコンピュータを結合してひとまとまりのシステムにしたもの。「コンピュータクラスタ」。ユニット間は高速なバス(最近は高速はクロスバースイッチが多い)で接続されている。メインフレームやスーパーコンピュータでよく採用されている

CPUのシステム構成

| MIMD | 複数のマイクロプロプロセッサを搭載した並列コンピュータ上で、複数のプロセッサが複数の異なるデータを並列処理する方式(マルチプロセッサが該当) |

|---|---|

| MISD | 並列コンピューティングアーキテクチャの一種であり、多数の機能ユニットが同じデータに対して異なる操作を同時に行う。パイプライン処理はその一例 |

| SIMD | マイクロプロセッサにおいて、1つの命令で複数のデータを扱う処理方式。DSPやスーパーコンピュータで利用される |

| SISD | マイクロプロセッサにおいて、1つの命令で1つのデータを扱う処理方式 |

アーキテクチャ

アーキテクチャ

アーキテクチャ

ハードウェアやソフトウェアの基本設計や設計思想のこと

RISC(Reduce Instruction Set Computer:縮小命令セットコンピュータ)

個々の命令を簡略化することによりパイプライン処理(並行して複数の命令を処理する方式)の効率を高め、処理性能の向上をはかっている

RISCアーキテクチャの特徴としては

固定命令語長

固定命令語長

命令の解読に際して可変長命令では命令長の判別と切り出し等に時間がかかっていた欠点を排除し、命令デコードに要する時間を短縮すると共に、命令の先読みをしてパイプラインの効率を上げる

全ての演算は1クロックで実行する

全ての演算は1クロックで実行する

パイプライン動作にウエイトを生じさせない

演算はレジスタ‐レジスタ間演算のみ

演算はレジスタ‐レジスタ間演算のみ

回路構成の単純化を図るとともに、メモリ・アクセスのレイテンシがパイプライン動作に悪影響を与えるのを避ける。メモリに影響する命令はロード・ストア命令のみであり、通常メモリ上のデータへの明示的な演算は行われない

ワイヤードロジックで構成

ワイヤードロジックで構成

マイクロコードによる命令実行(マイクロプログラム方式)を排し、命令実行に要するクロックサイクル数を削減するとともに、命令解析・実行を行う回路をゲートの組み合わせで実装し、高クロック動作を可能にする

多数のレジスタを備える

多数のレジスタを備える

演算の途中結果をCPU内に蓄えられる様にして、メモリへのアクセスを減らし、メモリ・アクセスによるレイテンシで動作が遅延するのを避ける

遅延実行スロットを備える

遅延実行スロットを備える

パイプラインハザードを避け、パイプラインの処理効率を上げ

CISC(Complex Instruction Set Computer:複合命令セットコンピュータ)

個々の命令を高級言語に近づけ、複雑な処理を実行できるようにすることで処理能力の向上をはかっている

単一の命令で複数の処理を行い、可変長命令、直行性がある、演算命令のオペランドにメモリを指定できる

マイクロプログラム制御方式

マイクロプログラム制御方式

、プロセッサの制御装置の実装手法のひとつ、CPU内のマイクロプログラムを使用して、複雑な命令を比較的容易に実装する

利点は、オペレーティングシステムを含めたソフトウェアから見た場合のハードウェアを、容易に追加・拡張、あるいはプロセッサ間で標準化して互換性を高める、更には異なる命令セットのCPUのエミュレートにも応用可能(仮想化技術のひとつともいえる)

反面、複雑な命令の増加はパイプラインの効果が薄れる結果ともなりやすい

CISCのCPUで採用されている